# 产业链协同创新的数字化实践

## 致力于更好的开放指令 (RISC-V) 商业IP设计和解决方案开发

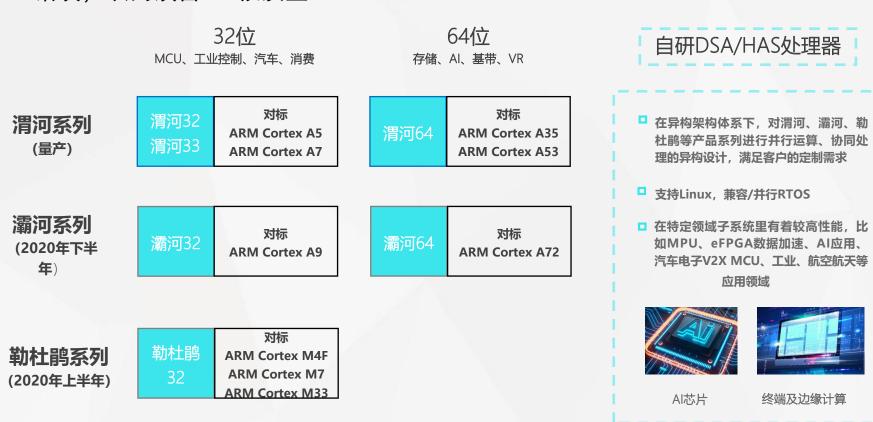

优矽科技是一家以RISC-V开源指令集为基础,进行处理器微架构研发,交付软件、硅知识产权及芯片级应用解决方案的科技创新企业。2017年加入RISC-V基金会,2018年3月在深圳建立应用研发中心,2020年荣获中国开放指令生态联盟"IP先锋奖",致力于成为自主知识产权微架构及其商业解决方案的领导者。

## 国产芯片实现自主可控的重大机遇

#### 半导体行业发展绊脚石----x86和ARM架构

- 架构专利属国外公司私有,国产芯片命脉受制于人

- □ 授权费、版税费极其**高昂**,非一般公司或组织可以承受

- □ 仅架构篇幅就达**数千页**,且指令数目复杂繁多,积重难返,硬件实现难度高

- 口 指令缺乏模块化,同一架构不同系列难以兼容

#### 不痛不痒的其他开源架构

- OpenRISC,侧重实现一种开源的CPUCore,非立足于 定义一种开放的指令集架构,所有的指令集改动都必须 开源,繁琐且混乱

- □ SPARC,初衷面向服务器领域,功耗及面积大,不适用 于PC与嵌入式领域,且不具备模块化的特点,难以作为 通用的处理器架构对x86和ARM架构形成替代

#### 国产芯片自主可控的架构----RISC-V

- □ 一种**完全开放**的指令集,可以被任何机构或组织自由使用

- □ 授权及版税费极低,IP**商业化取决于工艺技术**而非版权垄断

- □ **架构精简**,指令集文档和特权架构文档的篇幅也仅为100页

- □ 模块化指令,不同模块组合应用多样应用场景

#### RISC-V是极其优异的开源架构

- □ 极简、模块化和可扩展特性,使低功耗、小面积、个性化的定制芯片成为可能,并**突破摩尔定律极限**

- □ RISC-V基金会**统一管理**开源IP及指令集,适合硬件实现且稳定;3月份基金会从美国迁移至瑞士将更加有利于指令集规范与标准的开放开源中立的演进发展

- □ 面向多场景处理器应用,可在短时间建立芯片生态格局

## RISC-V设计理念大道至简,符合CPU处理需求发展

RISC-V最大的特性就在于"精简"。虽然与ARM同属于精简指令集架构,但因RISC-V是近年来才推出,没有背负向后兼容的历史包袱,架构短小精悍。相比于x86和ARM动辄几百数千页,RISC-V的规范文档仅有145页,且"特权架构文档"的篇幅也仅为91页

## RISC-V软硬件生态发展的挑战与机会

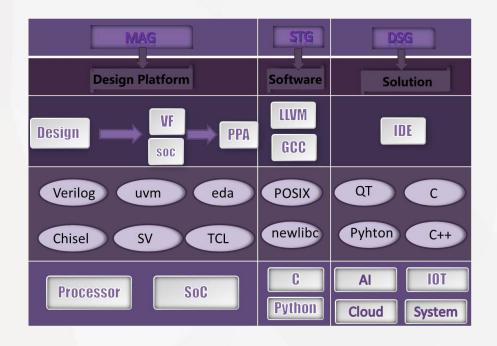

#1 生态建设当前主要挑战是软件/工具链业态和物理/硅业态的国产化与成熟化建设 #2 基于RISC-V体系结构底层技术和应用场景紧耦合的量产芯片定义设计制造与市场销售体系 #3 基于开放指令(RISC-V)中国基础研究平台和全球化中立合作联盟

#4 Semico Research 《RISC-V市场分析: 新兴市场》

- 预计到2025年,市场将总共消费624亿个 RISC-V CPU内核,其中预计工业领域将 是最大的细分市场,拥有167亿个内核

- RISC-V CPU内核的复合年增长率 (CAGR) 在2018年至2025年之间的平均 复合年增长率将高达146.2%

## 产业链合作伙伴 - 如何更好的进行协同创新

## 促进更好更快的开放指令生态发展

#### 软件公司

基于操作系统和应用 场景的软件开发

开发低功耗TWS蓝牙芯

片IP核

#### 芯片上市公司

全面替代和差异化补充 ARM Cortex-A7、A9、 A35、A53、A72 IP以及 基于Linux的SoC芯片联 合开发

#### **Perf**XLab

渭河WH32 bitstream版

权

开发AI算法

#### 一线晶圆厂

28/22nm及16/14/12nm 战略合作

深圳MCU芯片公司

基于勒杜鹃系列IP开发 MCU产品

#### 蓝牙芯片公司

开发基于RISC-V 的APU IP

基于WH32 bitstream开 发板进行项目科研 基于公司IP内核进行定制开发 应用于国家科研项目

## 为什么要改变

方法学与工具演进 开发与管理效率 知识产权对世界发展的影响守护 人类自然语言的物理描述及演进

机器语言 计算机体系结构:软硬件系统接口描述规范与标准 指令集及微架构处理器内核

## 布局布线技术的演进

1995

2015

2025

#### 以门为中心的设计方法

#### 以布局为中心的设计方法

#### 以布线为中心的设计方法

350nm 180nm 130nm 90nm 65nm 40nm 28nm 20nm 16nm 10nm 7nm 5nm 3nm

- 1. 设计的时序以 门延时 为主

- 综合工具得到的时序很容易在布局布线阶段满足

- 3. 此时的布局布线工具突出最小的芯片面积和运行时间

- 1. 随着器件尺寸的缩小,门 的电容也跟着减小

- 2. 线电容 成为时序的主要部分

- 布局的质量常常成为最终 决定设计时时序的关键所 在

- 4. 布局布线工具突出处理最优面积和功耗的快速设计收敛特性

- 随着线宽的缩小,线电阻成几何指数的增长

- 2. 线/孔电阻 成为时序的主要部分

- 详细绕线,以及pin的连接影响时序、IR和EM

- 如果没有在整个流程中清楚地考虑 详细绕线,则无法保证设计收敛

### 应对后摩尔时代的技术发展需求

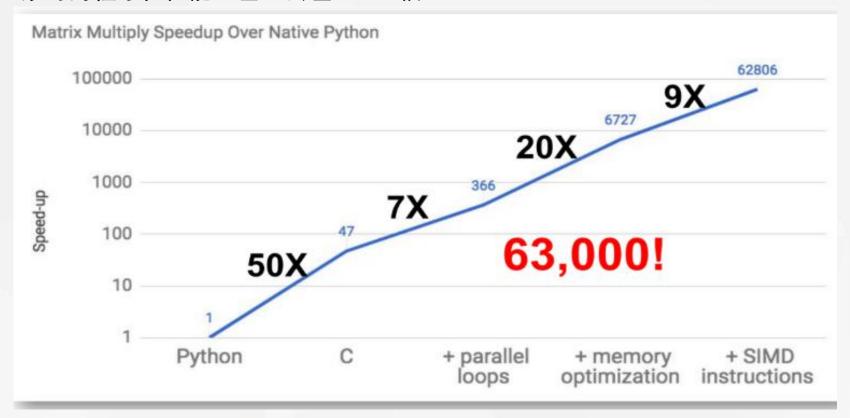

摩尔定律逐渐走向终结,但摩尔定律赋予芯片的能力并未充分挖掘出来。如图所示,以实现一个矩阵乘法为例,普通程序员写的程序和懂体系架构的专家写的程序在性能上甚至会差63000倍。

因此,如果将面向某个特定领域的专家知识实现到芯片中,就有可能将性能功耗比提升几百甚至几千倍,从而充分挖掘芯片上晶体管的潜力。但这种领域专用体系结构 (DSA) 会带来碎片化问题,需要从芯片设计成本与周期两个维度同时降低门槛,才能应对种类繁多的领域专用加速器。

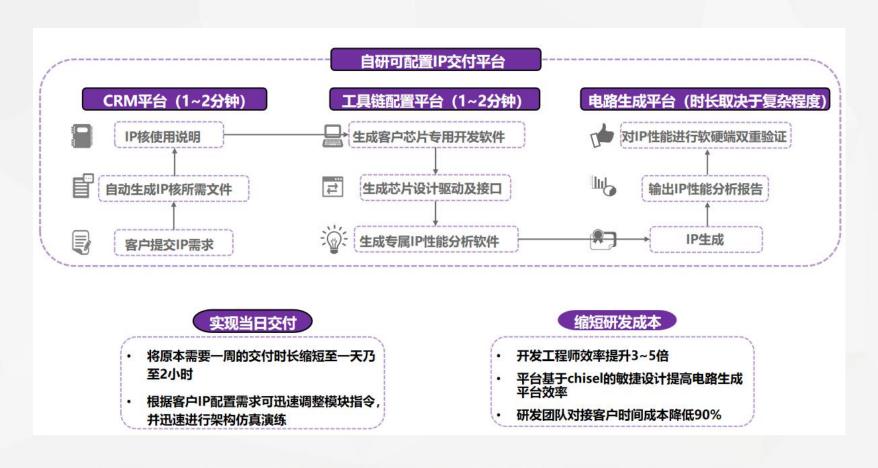

## 敏捷开发 - uBright 数字化IP交付平台

### 基于敏捷设计有效降低开发成本及缩短开发周期

自研uBright 平台结合Chisel硬件描述语言敏捷设计方法学实现IP产品快速交付,客户可通过IP库配置选型,将原本需要一周的交付时长缩短至一天乃至2小时,自动化生成平台大幅度缩减人力成本及开发周期,降低IP开发费用,为客户提供优质且高性价比的RISC-V IP处理器内核

## 如何提升RISC-V的快速发展路径

RV Foundation 基金会 - 中立开放开源永续发展的基石Bedrock

工作组和会员WG and Membership bylaw, by-teamwork, by-innovation, by-collaboration, by-contribution

- 技术开源 ←→ 商业闭源 RISC-V<sup>+</sup> as a Service 学术及产业链协同 创新推力 Innovation Thrust

- 商业量产迭代 问题解决者 Problem Solver 带不带入新问题?

人才与市场转化、技术与产品转化 让工程师文化彰显、让技术散发人性光辉

## 基于RISC-V开放指令集 → 商业闭源开发

基于chisel具有更高抽象的硬件描述语言设计方法学,实现基于一套源代码同时生成用于测试的仿真模拟代码以及用于流片的代码,提高测试效率,快速定位错误,从而改善 IP 核质量

通过硅验证实现 IP 核与工艺库高效对接的流程,推进 IP 核达到可流片的成熟度,并通过建立快速流片认证与测试机制,赋能客户产品快速量产及高效市场投放

## 教产学研一体化,人才实战培养,团队能力建设

优矽科技RISC-V自研产品不仅于商用,同时也通过与教育产业合作,推动产学研一体化发展,培养国内新一代集成电路设计技术人才,目前我司已与多所高校达成合作,其中包括深圳大学、西安电子科技大学、西安交通大学、西北工业大学等,且已与部分高校达成研究生课程教学合作

P1

开发板 Development Board RISC-V 64bit、RTOS and Linux

深圳大学 Shenzhen University

P2

P3

55LL、RV32IMCF

**Domain-Specific Architecture research**

可信计算模块 Tursted Compute Module

D and P proposals

SD、UART、ETHMAC、OLED、CAN、QSPI西安电子科技大学 Xi'dian University

**ML Data Acceleration**

22ULP RISC-V 64/32bit Linux MPU西安交通大学 Jiaotong University and

**Lead Partners**

**Lead Partners (eFPGA)**

## 技术创新, 商业迭代

## 核心合作伙伴 --应用场景1 工业级芯片设计制造厂商

#### 工业级国产芯 更稳定

4\*A7 1.2GHz+Mali400MP2 工业品质,100ppm,工作温度-40-85℃ 供货>10年

#### 为工控而生 赋能行业

A40i-Industrial Control Processor

#### 助力AI视觉应用

CSI0+CSI1+4\*CVBS IN+TS\*2 支持多达8路摄像头输入 支持单目/双目人脸识别应用

#### 接口丰富 成本更优

USB2.0\*3

GMAC+EMAC双网口可同时工作 SATA2.0/UART\*8/SPI\*4/

I2C\*5/RTP/PS2/IR

#### 点屏神器 无需转接

支持双RGB/双LVDS/MIPI DSI/ HDMI/CVBS/YPbPr/VGA显示 支持双屏(1080P)异显

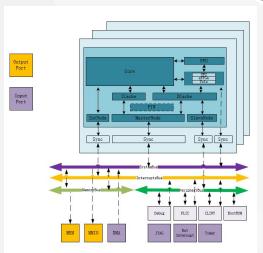

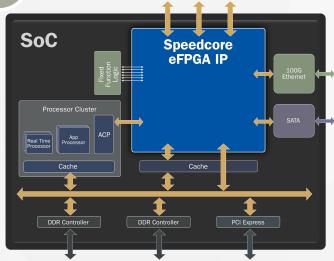

## 战略合作伙伴 嵌入式 FPGA

CPU + eFPGA + MLP 提供数据加速和适合算力匹配的基础设施应用场景:

- 1. 数据中心-计算、网络、存储

- 2. 5G无线基础设施 (通讯)

- 3. 有线网络

- 4. 汽车、工业、自动化等

产业链协同创新 - 共赢合力 实现处理器微架构、芯片系统与软件的自主可控、安全可信、国产替代

### 协作倡议举例

- 1. 基于Linux最小系统的可配置芯片级硬件设计

- 2. 亚阈值超低功耗标准单元库处理器优化包组合

## 感谢交流、期待合作

优矽科技 深圳市南山区高新区科园路2002号卫星大厦808室 https://www.uctechip.com